Mit dem Atari ST steht dem Anwender ein leistungsfähiger Rechner mit einer Vielzahl von Schnittstellen zur Verfügung. Dieser Rechner ist jedoch kein offenes System wie beispielsweise der IBM-PC oder der altbewährte APPLE, die beide mit ihrem Slot-System den jeweiligen Bedürfnissen angepaßt werden können.

Beim ST ist es sehr aufwendig, einen I/O-Port anzuschließen. Alternativen sind das Bussystem der Firma Rhothron oder eine Erweiterung am Modul-Port, die jedoch recht kompliziert ist, da leider beim ST am ROM-Port nur gelesen werden kann. Mancher Anwender schreckt vor den hohen Anschaffungskosten zurück.

Für Anwender, die keine Festplatte besitzen, bietet sich die hier vorgestellte preisgünstige Alternative an.

Sie bietet je 16 Ein- und Ausgabekanäle und kann bei Bedarf kaskadiert werden. Angeschlossen wird dieser I/O-Port an die DMA-Schnittstelle, er benötigt nur eine 19polige Steckverbindung mit entsprechendem Kabel.

Mit dieser Schaltung können elektrische Maschinen und Modelleisenbahnen gesteuert werden. Auch eine Meßdatenerfassung (Logik Analysator, A/D-Wandler) kann nun einfach und preiswert realisiert werden. Der Phantasie sind keine Grenzen gesetzt.

Programmiert wird diese Schnittstelle relativ einfach. Bedingung ist nur, daß die CPU in der Supervisor-Modus geschaltet wird. Ferner ist die Kenntnis des DMA-Chip auf der Rechnerplatine Voraussetzung. Dieser Chip wird deshalb ebenfalls in unserem Bericht beschrieben.

Die Hardware

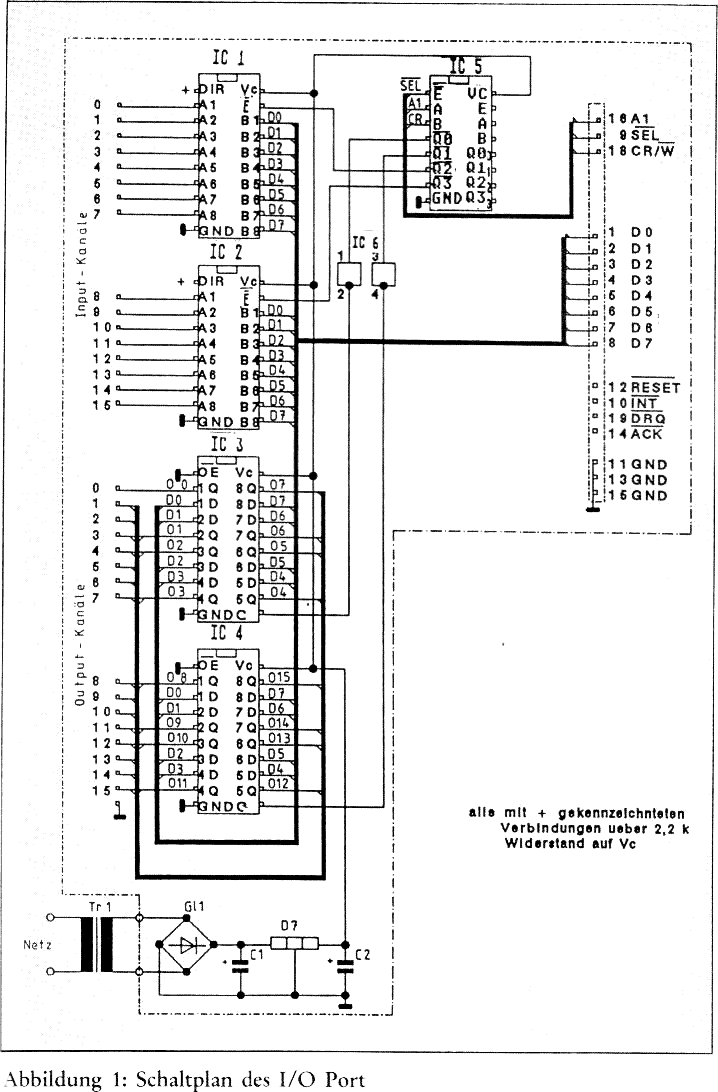

Die DMA-Schnittstelle ist das Bindeglied zu diesem Interface. Trotz der 16-Bit Architektur der CPU hat diese Schnittstelle nur 8-Bit-Format. Zusätzlich findet man die Leitungen Al, SEL, CR/W. Mit Al kann eine Adresse angewählt werden, SEL selektiert einen Controller und CR/W bestimmt die Richtung der Datenübertragung. Die verbleibenden Leitungen sind für die Funktion des Interfaces unwichtig.

Die 16 Eingabekanäle werden durch zwei 74LS245 gebildet, die die Daten auf den DMA-Bus schalten, wenn das entsprechende IC selektiert wurde.

Die 16 Ausgabekanäle werden durch zwei 8-Bit-Tri-State-Latches gebildet, so daß ausgegebene Daten gespeichert werden.

Die Freigabe der jeweiligen ICs geschieht unter Verwendung des Decoders 74LS139. Dieser Decoder selektiert die entsprechenden Register unter Verwendung der Eingangssignale Al, SEL, CR/W.

Alle Datenleitungen führen auf den DMA-Bus, so daß ein lokales Bussystem verwirklicht ist. Der große Vorteil besteht in der leichten Beschaff-barkeit der notwendigen ICs und im niedrigen Preis, da auf Spezialbauteile (z. B. programmiert PALSs) verzichtet wurde.

Um die entsprechenden Register anwählen zu können, muß man einige Register und Bits des DMA-Chip kennen.

Wichtig ist das DMA-Mode/Status-Register unter der Adresse SFF8606.

Beim Lesen des Registers enthalten die unteren drei Bits folgende Bedeutung:

Bit 0:

1 Fehler bei der DMA-Übertragung aufgetreten

0 Kein Fehler

Bit 1:

1 Sektor Count Register ist < > 0

0 Sektor Count Register ist Null

Bit 2:

Zustand des Data Request Signals an der Schnittstelle

Wird nun auf diese Adresse geschrieben, so haben die einzelnen Bits folgende Bedeutung:

Bit 0:

Findet keine Verwendung

Bit 1:

Adresse A0; 0 = Pin A0 ist low

1 = Pin A0 ist high

Bit 2:

Adresse A1; 0 = Pin A1 ist low

1 = Pin A1 ist high

Bit 3:

0 = Zugriff auf Floppy Disk Controller

1 = Zugriff auf Hard Disk Controller

Bit 4:

3 = Zugriff auf Floppy Disk Controller-Register

1 = Zugriff auf Sektor Count Register

Bit 5:

Findet keine Verwendung

Bit 6:

0 = DMA einschalten

1 = DMA ausgeschaltet

Bit 7:

0 = Zugriff auf Hard Disk Controller

1 = Zugriff auf Floppy Disk Controller

Bit 8:

0 = HDC/FDC lesen

1 = HDC/FDC schreiben

Das Datenregist er ist unter der Adresse SFF8604 zu erreichen. Wichtig ist in diesem Zusammenhang die Systemvariable „flock“ $43E, die benötigt wird, um die Floppy zu sperren.

Ferner ist die Beschaltung des Decoders 74LS139 von Bedeutung:

| SEL |

AI |

CR/W |

|

| 0 |

0 |

0 |

Register IC3 aktiviert Output 0-7 |

| 0 |

0 |

1 |

Register IC1 aktiviert Input 0-7 |

| 0 |

1 |

0 |

Register IC4 aktiviert Output 8-15 |

| 0 |

1 |

1 |

Register IC2 aktiviert Input 8-15 |

| 1 |

0 |

0 |

Sämtliche IC inaktiv |

| 1 |

0 |

1 |

Sämtliche IC inaktiv |

| 1 |

1 |

0 |

Sämtliche IC inaktiv |

| 1 |

1 |

1 |

Sämtliche IC inaktiv |

Die Software

Durch diese Hardwarekonfiguration ist es möglich, die Ports zu programmieren. Dabei empfiehlt sich folgendes Schema:

Die CPU wird in den Supervisor-Mode geschaltet, da dieser Adressbe-reich intern im User-Mode geschützt ist. Anschließend ist die Systemvariable „flock“ auf den richtigen Wert zu bringen. Die Programmierung des DMA-Mode-Registers bestimmt das Portregister, ein Lese- bzw. Schreibbefehl aktualisiert die Daten. Die Systemvariablen „flock“ erhält wieder den Ausgangszustand und die CPU wird wieder in den User-Mode geschaltet.

In der Programmiersprache „C“ wird diese Arbeit zum Teil durch die Funktion $20 SUPER abgenommen.

Das abgedruckte Programm „OUTPUT 1“ zeigt ausführlich die zur Programmierung notwendigen Befehle. Besonders aufschlußreich ist dabei die Programmierung des DMA-CONTROL-Registers unter der Adresse $FFFF8606. Folgende Möglichkeiten sind dabei zulässig:

$188:

Ermöglicht das Anwählen des IC 3 für eine Ausgabe auf 00-07

$18E:

Ermöglicht das Anwählen des IC 4 für eine Ausgabe auf 08-015

$088:

Ermöglicht das Anwählen des IC 1 für eine Eingabe über 10-17

$08E:

Ermöglicht das Anwählen des IC 2 für eine Eingabe über 18-115

Die Zusammensetzung des betreffenden „Kontrollwortes“ zeigt die oben beschriebene Tabelle.

Die entsprechende Programmeinbindung zeigen die Listings, die sich hoffentlich selbst erklären. Listing 1 und 2 (Output 1 und 2) dienen zur Erklärung des Userports als Ausgang. Li-sting 3 und 4 (Input 1 und 2) dienen zur Erklärung des Userports als Eingang-

Um die Schaltung auf ihre Funktionsfähigkeit zu testen, kann das folgende Programm „Zaehlprogramm“ (Listing 5) verwendet werden. Es wurde mit dem SEKA-Assembler erstellt. Nach der Eingabe des Programms im Editor-Modus muß es assembliert werden. Gestartet wird das Programm mit „gstart“. Dann werden die Ausgänge 00-07 binär incrementiert und die Ausgänge 08-015 binär decremen-tiert. Das zugehörige Programmlisting ist wieder größtenteils selbsterklärend und demonstriert anschaulich die Funktion der Schaltung.

Für Programmierer, die nicht Assembler verwenden, bieten wir die gleichen Routinen, die sich in jedes Programm einbinden lassen, auch in GfA-Basic an. (siehe Listing 6, 7 und 8)

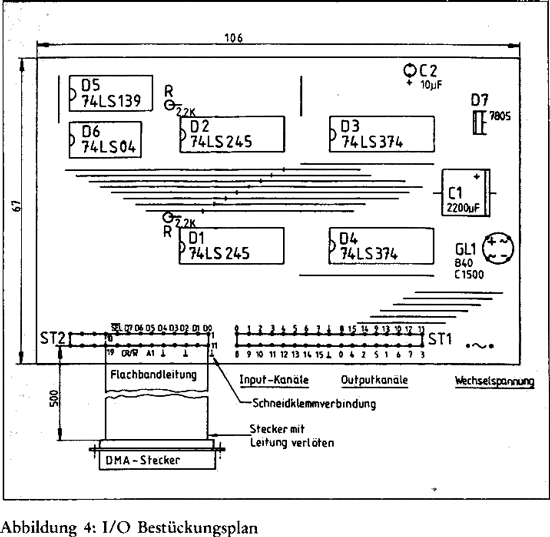

BAUTEILELISTE I/O-PORT

| IC1 | IC | 74LS245 | |

| IC 2 | IC | 74LS245 | |

| IC 3 | IC | 74LS374 | |

| IC 4 | IC | 74LS374 | |

| IC 5 | IC | 74LS139 | |

| IC 6 | IC | 74LS04 | |

| D7 | Spannungsregler | 7805 | |

| GH | Gleichrichter | B40 CI500 | runde Bauform |

| CI | Elko | 2200uF/18V | |

| C2 | Tantal Kondensator | 10uF/6V | |

| Tri | Netztrafo | ca. 11V/0.5A | |

| R | Widerstand | 2,2K | 2 Stück erforderlich |

| Stl | Pfostenstecker | 34pol | 2reihig |

| St2 | Pfostenstecker | 26pol | 2reihig |

| Buchsenleiste zu ST2 | | mit Zugentlastung |

| Flachbandleitung | 19polig | ca. 0,5 m |

| DMA-Stecker | 19polig | siehe Bezugsquelle |

| IC-Fassung | 20polig | 4 Stück erforderlich |

| IC-Fassung | 16polig | |

| IC-Fassung | 14polig | |

| gedruckte Schaltung | | siehe Bezugsquelle |

| Schaltdraht | 0,8 mm 0 | versilbert |

Abbildung 2: Bauteileliste

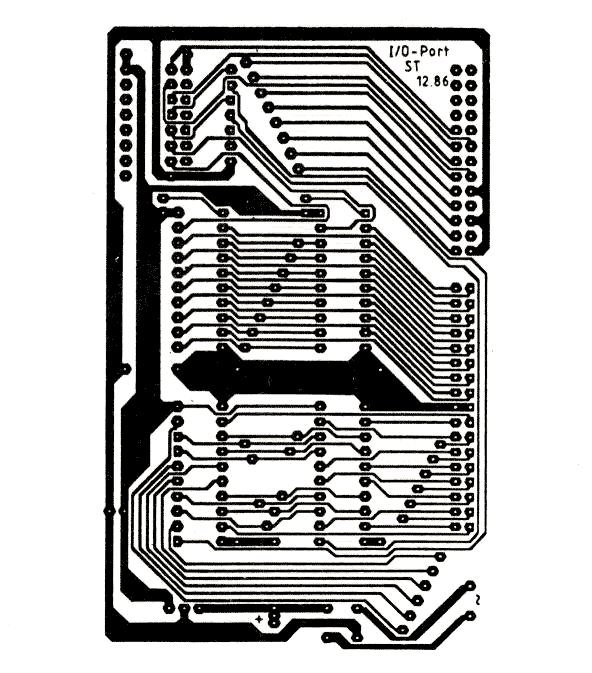

Das Layout

Das abgebildete Layout der Schaltung vereinfacht den Aufbau. Dieses Layout ist nur für Bastler gedacht, die mit geringem finanziellem Aufwand diede Platine realisieren möchten. Für Anwender, die weniger Erfahrung im Aufbau von elektronischen Schaltungen hat, wird vom HEIM-Verlag eine doppelseitige Platine angeboten. Bei unserem einseitigen Layout sind gemäß dem Bestückungsplan einige Drahtbrücken zu ziehen. Dieses hat den Vorteil, daß die Platine einfacher und preiswerter herzustellen ist als eine doppelseitige Platine. Die zur Bestückung notwendigen Bauteile und Materialien sind in der Stückliste zusammengefaßt.

Doch nun zum praktischen Aufbau der Platine. Zuerst sollten alle notwendigen Drahtbrücken eingelötet werden. Dabei muß in der Mitte der Platine darauf geachtet werden, daß ein dünner Schaltdraht verwendet wird, da zwei Drähte durch eine Bohrung passen müssen. Dies ist im Bestückungsplan durch einen kleinen, senkrechten Strich gekennzeichnet.

Anschließend sollten alle IC-Fassungen eingelötet werden, wobei wir aus Gründen der Kontaktsicherheit gedrehte Fassungen bevorzugen.

Abbildung 3: Platinen Layout (Lötseite)

Abbildung 3: Platinen Layout (Lötseite)

Danach sind die Pfostenstecker und die restlichen Bauteile einzulöten. Dabei bitte auf die Bauformen des Brückengleichrichters (rund) und des Eikos Cl achten! Der notwendige Netztrafo sollte ca. llV/500mA liefern. Der Wechselspannungsanschluß ist gekennzeichnet.

Das 19polige Verbindungskabel wird an den DMA-Stecker angelötet. Die Verbindung zur Platine geschieht mit einer 26poligen Buchsenleiste in Schneidklemmtechnik. Flachbandkabel bündig auf der rechten Seite (siehe Bestückungsplan) in die Buchse legen und die Verbindung hersteilen. Eine andere Möglichkeit ist das direkte Verlöten der Flachbandleitung.

Alle Ein- und Ausgänge der Schaltung liegen auf der 34poligen Pfostenleiste. Es ist darauf zu achten, daß alle Eingangssignale TTL-Pegel aufweisen und daß an die Ausgänge keine LEDs direkt angeschlossen werden können, da IC 3 und IC 4 nicht genügend Strom liefern. Die Zwischenschaltung eines Treibers ist also notwendig.

Sollen mit dem Interface Netzgeräte geschaltet werden, so ist eine galvanische Entkopplung aus Sicherheitsgründen unbedingt zu empfehlen.

Bezugsquelle

Alle Bauteile sind im Elektronikhandel leicht erhältlich. Eine doppelseitige Platine ist für DM 38,- plus Versandkosten beim Heim-Verlag zu beziehen. Der DMA-Stecker wird von der Fa. Lischka Datentechnik, Hochstraße 22 in 4173 Kerken geliefert.

# Der DMA-Controller

DMA steht für Direct Memory Access, zu deutsch direkter Speicherzugriff. Ein DMA-Controller stellt das Bindeglied zwischen Speicher und Peripheriebausteinen dar. Verschiedenartige Geräte können an den DMA-Controller angeschlossen werden, z. B. Floppies, Magnetbänder, Drucker oder Harddisk. Der DMA-Controller wird vom Prozessor wie ein ganz normaler Speicherbaustein angesprochen. Der Prozessor bestimmt, ab welcher Adresse die Daten abgespeichert werden sowie die Menge der Daten. Insofern entlastet der DMA-Controller die CPU, da er selbständig die Daten aus dem Speicher herausliest und diese sehr schnell nach außen weiterleitet. Außerdem kann der Controller die Adressierungen für die verschiedenen Peripheriebausteine liefern. Der DMA-Controller beim ST ist einer der vier von ATARI selbst hergestellten Chips und dient zur Ansteuerung von Floppies, Harddisk und für die Zukunft geplanten Peripherie-Geräten. Er ist neben dem Video-Shifter der einzige Baustein, der mit 16 Feitungen am Datenbus hängt.

Der Speicherbereich des DMA-Controllers

Alle I/O-Bausteine belegen die obersten 32 KByte des Adressbe-reichs. Der DMA-Controller liegt im Adressbereich von SFF8600 bis SFF860D.

$FF8600

reserviert

$FF8602

reserviert

$FF8604

Daten Register

$FF8606

Mode/Status Register

$FF8609

DMA Basis und Zähler High-Byte

$FF860B

DMA Basis und Zähler Mid-Byte

$FF860D

DMA Basis und Zähler Fow-Byte

In den drei zuletzt genannten Registern muß z. B. die Adresse eingetragen werden, wohin die Daten beim Fesen von der Festplatte gespeichert werden sollen.

Die Bausteine unseres Userports

Um den Harddisk-Anschluß des ATARI ST für andere Zwecke zu benutzen, ist ein gewisser Aufwand an Elektronik notwendig. Auf der Platine befinden sich verschiedene Bausteine, die wir hier kurz beschreiben möchten.

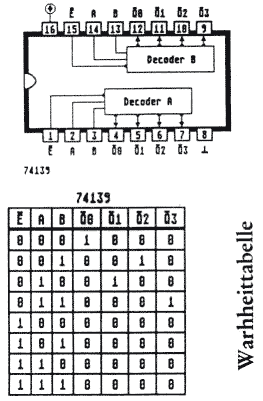

Der Decoder 74139

Dieser Baustein spielt eine große Rolle im gesamten Hardware-Konzept des Userports. Der 74139 enthält zwei getrennte l-aus-4-Decoder. Bei der Realisierung unserer Karte wird aber nur eine Hälfte des Bausteins benötigt. Der Decoder wird mit der Software gesteuert und dient zur Selektierung der verschiedenen Bausteine. Zwei acht Bit Zwischenspeicher (74374) und zwei acht Bit Bus-Leistungtreiber (74245) werden von diesem Decoder je nach Zustand der Auswahlleitungen (A und B) sowie dem Enable Eingang E (Freigabe) angesprochen bzw. aktiviert. Zum besseren Verständnis liefern wir Ihnen eine Wahrheitstabelle des Decoders. Aus dieser Wahrheitstabelle kann man ersehen, welcher der vier Ausgänge je nach Zustand der drei Eingänge aktiviert wird.

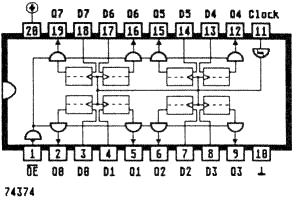

Der Zwischenspeicher 74374

Dieser Baustein enthält acht flankengetriggerte D-Flipflops, die zur Speicherung der Daten, die ausgegeben werden sollen, dienen. Die an den Eingängen (DO bis D7) anliegenden Daten werden beim Low-High-Übergang (positive Flanke) des Taktes am Clock-Anschluß in den Flipflops gespeichert. Die gespeicherten Daten erscheinen an den Ausgängen Q, wenn der Freigabe-Eingang OE (Output Enable) auf Low-Potential liegt. Folglich werden die gesendeten Daten solange gespeichert, bis eine neue positive Flanke an den Clock-Eingang gelangt.

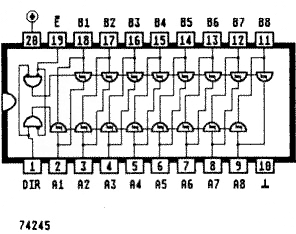

Der Bus-Leitungstreiber 74245

Dieser Baustein enthält acht bidirektionale Bus-Leitungstreiber. Bei unserem Userport werden Daten aber nur in eine Richtung verstärkt, da der DIR-Eingang (Direction) fest auf Masse gelegt ist. Dieser Baustein dient folglich zur Verstärkung der acht Eingangssignale und gleichzeitig zum Schutz des Rechners. Der Freigabe-Eingang E muß auf Low-Potential liegen, damit die Daten übertragen werden, ansonsten sperrt der Chip die Verbindung.

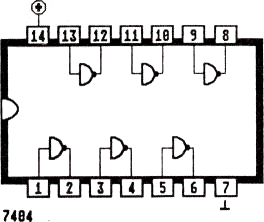

Der Sechsfach-Inverter 7404

Der Baustein mit der Bezeichnung 7404 enthält sechs getrennte Inverter. Sie können unabhängig voneinander verwendet werden. Auf dieser Platine werden zwei davon gebraucht, um die Selektleitung der Decoder zu invertieren.

;***********************************************

;* I/O-Port fuer ATARI ST-Sene *

;* Thomas Blome Im Tiefen Winkel 3a *

;* 5750 Menden 1 *

;***********************************************

;* SEKA ASSEMBLER *** September 1986 *

;***********************************************

;* PROGRAMMNAME: OUTPUT 1 *

;* Programm schaltet CPU in den SUPER-Mode *

;* und gibt die in Register D2 stehenden Daten *

;* auf Port 00-07 aus *

;* Anschliessend wird die CPU in den USER-Mode *

;* geschaltet *

;***********************************************

dmadata: equ $ffff8604 ;Daten Register

dmamode: equ $ffff8606 ;Mode Control Register

flock : equ $43e ;DMA chip lock variable

savesp: equ $000f4000 ;Stack retten

;**********************************************

:* CPU in SUPER-MODE schalten *

;**********************************************

start: clr.l —(sp)

move.w #$20,-(sp)

trap #1

add.l #6,sp

move.l d0,savesp

st flock ;lock DMA

;**********************************************

;* Zugriff nun auf DMA-Port moeglich *

;**********************************************

lea dmamode,a6

lea dmadata,a5

move.w #$0f,d2 ;Daten in Register D2

move.w #$188,(a6) ;Port Register anwaehlen

move.w d2,(a5) ;Daten auf 00-07 ausgeben

;**********************************************

;* CPU in USER-MODE schalten *

;**********************************************

move.l savesp, -(sp)

move #120, -(sp)

trap #1

add.l #6,sp

end

;**********************************************

Listing 1

;**********************************************

;* I/O-Port fuer ATARI ST-Serie *

;* Thomas Blome Im Tiefen Winkel 3a *

;* 5750 Menden 1 *

;**********************************************

;* SEKA ASSEMBLER *** September 1906 *

;**********************************************

;* PRQGRAMMNAME: OUTPUT 2 *

;* Programm schaltet CPU in den SUPER-Mode *

;* und gibt die in Register D2 stehenden Daten*

;* auf Port 08-015 aus *

;* Anschliessend wird die CPU in den User- *

;* Mode geschaltet *

;**********************************************

dmadata: equ $ffff8604 ;Daten Reqister

dmamode: equ $ffff8606 ;Mode Control Register

flock : equ $43e ;DMA Chip lock variable

savesp: equ $000f4000 ;Stack retten

;**********************************************

;* CPU in SUPER-MODE schalten *

;**********************************************

start: clr.l -(sp)

move.w #$20,-(sp)

trap #1

add.l #6,sp

move.1 d0,savesp

st flock ;lock DMA

;**********************************************

;* Zugriff nun auf DMA-Port moeglich *

;**********************************************

lea dmamode,a6

lea dmadata,a5

move.w #$55,d2 ;Daten in Register D2

move.w #$18e,(a6) ;Port Register anwhlen

move.w d2,(a5) ;Daten auf 08-015 ausqeben

;**********************************************

;* CPU in USER-MODE schalten *

;**********************************************

move.l savesp,-(sp)

move #$20,-(sp)

trap #1

add.l #6,sp

end

;**********************************************

Listing 2

;**********************************************

;* I/O-Port fuer ATARI ST-Serie *

;* Thomas Blome Im Tiefen Winkel 3a *

;* 5750 Menden 1 *

;**********************************************

;* SEKA ASSEMBLER *** September 1906 *

;**********************************************

;* PROGRAMMNAME: INPUT1 *

;* Programm schaltet CPU in den SUPER-Mode *

;* und liest Daten von IÖ-I7 in Register D2 *

;* Anschiieend wird die CPU in den USER-Mode *

;* geschaltet *

;**********************************************

dmadata: equ $ffff8604 ;Daten Register

dmamode: equ $ffff8606 ;Mode Control Register

flock : equ $43e ;DMA chip lock variable

savesp: equ $000f4000 ;Stack retten

;**********************************************

;* CPU in SUPER-MODE schalten *

;**********************************************

Start: clr.l -(sp)

move.w #120,-(sp)

trap #1

add.l #6,sp

move.l d0,savesp

st flock ; lock DMA

;**********************************************

;* Zugriff nun auf DMA-Port moeglich *

;**********************************************

lea dmamode,a6

lea dmadata,a5

move.w #$088,(a6) ;Part-Register anwaehlen

move.w (a5),d2 ; Daten von 10-17 laden

;**********************************************

;* CPU in USER-MODE schalten *

;**********************************************

move.l savesp,-(sp)

move #$20,-(sp)

trap #1

add.l #6,sp

end

;**********************************************

Listing 3

;**********************************************

;* I/O-Port fuer ATARI ST-Serie *

;* Thomas Blome Im Tiefen Winkel 3a *

;* 5750 Menden 1 *

;**********************************************

;* SEKA ASSEMBLER *** September 1906 *

;**********************************************

;* PROGRAMMNAME: INPUT2 *

;* Programm schaltet CPU in den SUPER Mode *

;* und liest Daten von 18-115 in Register D2 *

;* Anschiieend wird die CPU in den USER-Mode *

;* gesachaltet *

;**********************************************

dmadata: equ $ffff8604 ; Daten Register

dmamode: equ $ffff8606 ; Mode Control Register

flock : equ $43e ;DMA chip lock variable

savesp: equ $000f4000 ;Stack retten

;**********************************************

;* CPU in SUPER-MODE schalten *

;**********************************************

start: clr.l -(sp)

move.w #$20,-(sp)

trap #1

add.l #6,sp

move.l d0,savesp

st flock ;lock DMA

;**********************************************

;* Zugriff nun auf DMA-Port moeglich *

;**********************************************

lea dmamode,a6

lea dmadata,a5

move.w #$08e,(a6) ;Port-Register anwaehlen

move.w (a5),d2 ;Daten von 18-115 laden

;**********************************************

;* CPU in USER-MODE schalten *

;**********************************************

move.l savesp,-(sp)

move #$20,-(sp)

trap #1

add.l #6,sp

end

;**********************************************

Listing 4

;**********************************************

;* I/O-Port fuer ATARI ST-Serie *

;* Thomas Blome Im Tiefen Winkel 3a *

;* 5750 Menden 1 *

;**********************************************

;* SEKA ASSEMBLER *** September 1906 *

;**********************************************

;* PROGRAMMNAME: Zaehlprogramm *

;* LED am Ausgangspart werden binaer in- *

;* crementiert und decrementiert *

;**********************************************

dmadata: equ $ffff8604 ; Daten Register

dmamode: equ $ffff8606 ; Mode Control Register

flock : equ $43e ;DMA chip lock variable

savesp: equ $000f4000 ;Stack retten

hz200 : equ $4ba ;200hz counter

;**********************************************

;* CPU in SUPER-MODE schalten *

;**********************************************

start: clr.l -(sp)

move.w #$20,-(sp)

trap #1

add.l #6,sp

move.l d0,savesp

st flock ;lock DMA

;**********************************************

;* Zugriff nun auf DMA-Port moeglich *

;**********************************************

lea dmamode,a6

lea dmadata,a5

move.w #$ff,d2 ;Register D2 vorbesetzen

move.w #$0,d0 ;Register DO loeschen

wait1: move.w #$188,(a6) ;Ausgaberegister anwaehlen

move.w d0,(a5) ;aktuelle Daten auf 00-07 ausgeben

move.w #$18e,(a6) ;Ausgaberegister anwaehlen

move.w d2,(a5) ;aktuelle Daten auf 08-015 ausgeben

moveq #20,d1 ;Zeitverzgerung laden

add.l hz200,d1 ;

wait: cmp.l hz200,d1 ;

bne wait ;Warten bis Zeit abgelaufen ist

add.w #$1,d0 ;register D0 incrementieren

sub.w #$1,d2 ;Register D2 decrementieren

bra wait1

Listing 5

' OUTPUT 1

' Daten werden au-f Port 00—07 ausgegeben

For 1=1 To 9

Sdpoke &HFFFF8606, &H188

Sdpoke &HFFFF8604, I

Open "o", #1,"vid:"

Print #1,Chr$(16+I);

Print

Pause 10

Sdpoke &HFFFF8604,0

Close #1

Next I

Listing 6

' INPUT i

' Daten werden auf Port 10-17 gelesen

'

Sdpoke &HFFFF8604 , &H88

Print Dpeek (&HFFFF8606)

Sdpoke &HFFFF8604,0

Listing 7

' Zählerprogramm

' LED am Ausgangsport werden incrementiert

'

'

Dma=&HFFFF8604

Dmm=&HFFFF8606

A=9

E=20

B=16

Open "O",#1, “vid:"

Open "O",#2,"con:"

For 1=1 To 255

Sdpoke Dma,0

Sdpoke Dmm,2&H188

Sdpoke Dma,I

A$=Chr$(B+I)

If I>E-1 Then

E=E+10

A=A+10

B=B+1

Endif

If I>99 And I<101 Then

B$=Chr$(17)

B=15

Endif

If I>199 And I<201 Then

B$=Chr$(18)

B=15

Endif

If I>A And I<E Then

A$=B$+Chr$(B+1)+Chr$(15+I-A)

Endif

Print #2,Chr$(27);"Y";Chr$(43);Chr$(67);

Print #1,A$;

Print

Pause 5

Next I

Close

Listing 8